BỘ LỌC THÔNG DẢI CAO TẦN DẠNG HAIRPIN TRÊN CÔNG NGHỆ MẠCH DẢI MICROSTRIP

09:02 - 24/03/2020

Kỹ thuật siêu cao tần có rất nhiều ứng dụng trong công tác thiết kế và chế tạo các thiết bị cho hệ thống thông tin vô tuyến hiện nay như các hệ thống thông tin Viba và thông tin vệ tinh.

NGHIÊN CỨU THIẾT KẾ BỘ CHUYỂN ĐỔI CÁP ĐỒNG TRỤC - ỐNG DẪN SÓNG ỨNG DỤNG TRONG CÁC HỆ THỐNG THÔNG TIN SIÊU CAO TẦN

Kỹ thuật siêu cao tần có rất nhiều ứng dụng trong công tác thiết kế và chế tạo các thiết bị cho hệ thống thông tin vô tuyến hiện nay như các hệ thống thông tin Viba và thông tin vệ tinh. Trong khuôn khổ bài viết này tác giả chỉ giới thiệu đến một phần ứng dụng nhỏ, trong đó đề cập đến việc sử dụng đường truyền mạch dải để thiết kế và chế tạo các bộ lọc siêu cao tần.

Hiện nay các dòng IC cao tần thường có dải tần công tác lớn, từ hàng MHz lên đến hàng chục GHz (LNA, KĐCS, KĐ đệm, …), tuy nhiên thực tế ứng dụng các dòng IC này chỉ gói gọn trong dải tần công tác của thiết bị mà người thiết kế lựa chọn (chỉ khoảng vài trăm MHz), nên ở đầu vào hoặc ra của IC phải sử dụng các bộ lọc để nâng hiệu suất làm việc (nâng hệ số khuếch đại G). Ngoài ra ở đầu ra của các bộ trộn tần, hay ở đầu vào của các khối chức năng của thiết bị cũng rất cần các bộ lọc để lọc hài và nhiễu tín hiệu để thiết bị làm việc ổn định hơn.

Bộ lọc thông dải cao tần có thể thiết kế theo nhiều phương án khác nhau, trong đó có thể kể đến phương án sử dụng các phần tử tập trung là cuộn cảm L và tụ điện C. Với bộ lọc thông dải có tần số trung tâm 766MHz (dải sóng UHF), băng thông 60MHz với tổn hao trong và ngoài băng thông tương ứng là -5dBm và -60dBm chúng ta có thể lựa chọn bộ lọc thông dải dạng Chebyshev gồm 5 mắt lọc.

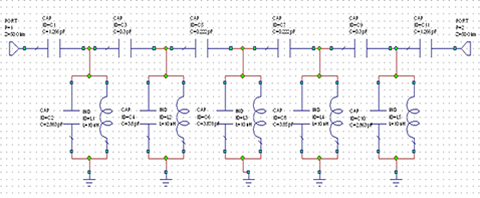

Trên các linh kiện tập trung L và C sơ đồ mạch nguyên lý của bộ lọc có dạng như sau (xem Hình 1):

Hình 1. Sơ đồ tương đương của bộ lọc trên các phần tử tập trung L và C

Từ mạch L và C tương đương chúng ta thấy rằng để chế tạo bộ lọc trên các phần tử tập trung là việc khó thực hiện vì không thể tìm được các linh kiện tụ điện có giá trị là 1.266pF, 0.222pF hay 3.878pF, đó là chưa kể đến các linh kiện tập trung thường có sai số dẫn đến các sai lệch khác về tần số. Để giải quyết các vấn đề này chúng ta có thể sử dụng các phần tử phân bố là đường truyền mạch dải.

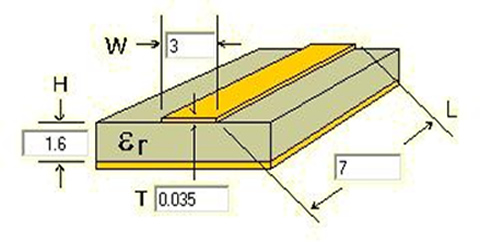

Trước hết chúng ta cần hiểu đường truyền mạch dải mà chúng ta dự kiến sử dụng để thiết kế bộ lọc mong muốn là gì? Đường truyền mạch dải (xem Hình 2) là các đường mạch in được dùng rất phổ biến trong các mạch siêu điện tử siêu cao tần. Các tấm điện môi dùng làm đế của mạch in có độ thẩm điện tương đối khá lớn Εr = 4 ÷ 13, có tiêu hao nhỏ và có độ dầy H = 0,5 ÷ 5mm. Để tạo ra các dải kim loại dẫn sóng, người ta dùng các kim loại phun, tạo ra trên mặt tấm điện môi các dải dẫn sóng có độ dày lớn hơn nhiều lần độ thấm sâu của trường T = 15 ÷ 100µm. Dải kim loại rộng gọi là bản đáy hay bản đất, còn dải hẹp có độ rộng W = 0,05 ÷ 10mm được gọi là dải trung tâm dẫn sóng. Độ rộng của mạch dải thường lớn gấp nhiều lần chiều cao tổng cộng của nó.

H, W, L – Độ dày, độ rộng và chiều dài của đường mạch in

H, W, L – Độ dày, độ rộng và chiều dài của đường mạch in

Εr – Độ thẩm điện tương đối của lớp điện môi

T – Độ dày của lớp kim loại dẫn hoặc bản đất

Hình 2. Đường mạch dải (Microstrip line)

Một số đặc tính của đường truyền mạch dải:

- Mạch dải có thể được sử dụng như là một đường truyền dẫn, tương đương với các linh kiện thụ động và mạch lọc;

- Mạch dải là đường truyền không cân bằng, có bức xạ điện từ nhưng rất nhỏ, do đó mạch dải thường dễ thực hiện và có nhiều ứng dụng;

- Mạch dải có trở kháng từ 10W đến 100W tùy người thiết kế, mạch dải 50W được sử dụng để phối hợp trở kháng;

- Mạch dải là linh kiện thụ động, tụ điện và biến áp phân bố có thể tạo ra từ các đoạn đường truyền mạch dải trên mạch in.

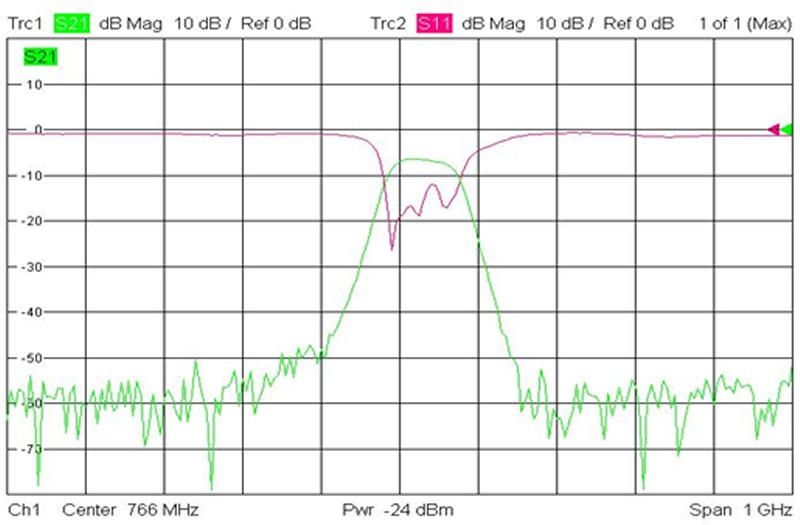

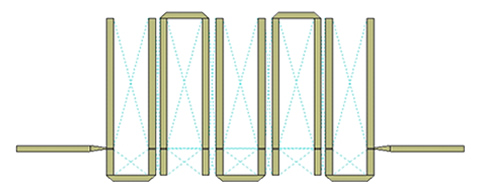

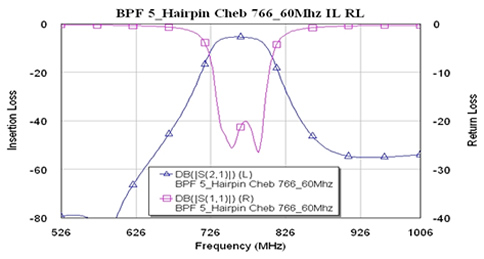

Trên phần mềm thiết kế mạch điện tử siêu cao tần (ADS, AWR, …) sơ đồ mạch nguyên lý tương đương dạng Hairpin sử dụng đường truyền mạch dải của bộ lọc với các thông số nêu trên (xem Hình 3) và đặc tuyến đáp ứng tần số của mạch tương đương này (xem Hình 4) có dạng như sau:

Hình 3. Sơ đồ tương đương dạng Hairpin của bộ lọc trên các phần tử mạch dải

Hình 4. Đáp ứng tần số của bộ lọc trên các phần tử mạch dải

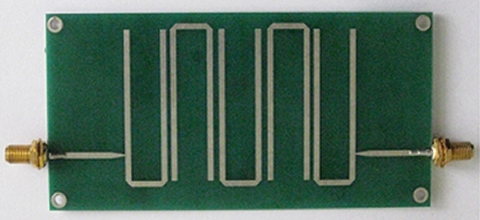

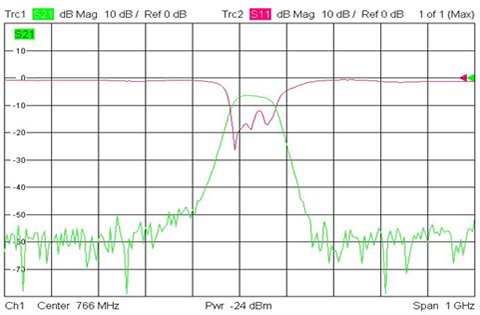

Trên cơ sở thiết kế và kết quả mô phỏng điện từ trường của đặc tuyến tần số bộ lọc chúng ta sẽ đi đặt gia công mạch in. Cần chú ý rằng mức độ chính xác trong gia công đường mạch in ảnh hưởng trực tiếp đến chất lượng của bộ lọc. Gia công với độ chính xác theo thiết kế càng cao thì đặc tuyến tần số của bộ lọc cang gần với kết quả mô phỏng trên phần mềm. Hình ảnh bộ lọc được chế tạo thực tế (xem Hình 5) và đặc tuyến đáp ứng tần số của nó (xem Hình 6) có dạng như sau:

Hình 5. Bộ lọc thực tế trên vật liệu mạch in RF4 (Bản dẫn và bản đất)

Hình 6. Đáp ứng tần số của bộ lọc thực tế

Tài liệu tham khảo:

- M.B. Bazdar, A.R. Djordjevic, R.F. Harrington, and T.K. Sarkar, "Evaluation of quasi-static matrix parameters for multiconductor transmission lines using Galerkin's method," IEEE Trans. Microwave Theory Tech., vol. MTT-42, July 1994, pp. 1223-1228.

- I. J. Bahl and D. K. Trivedi, "A Designer's Guide to Microstrip Line," Microwaves, p. 174, May, 1977.

- S. March, "Microstrip Packaging: Watch the Last Step," Microwaves, p. 83, Dec., 1981.

- G. Wells and P. Pramanick, Int. J. Microwave and mmWave Computer-Aided Design, Vol. 5, p. 287, 1995.

TS. Nguyễn Liêm HIếu

VIỆN IMC

Tòa nhà IMC Tower, Số 176 Trường Chinh, Phường Khương

Thượng, Quận Đống Đa, Thành phố Hà Nội, Việt Nam

Tel/Fax : (+84) 24 3566 6232 / 24 3566 6234

Email: contact@imc.org.vn Website: http://imc.org.vn